# Automotive Electronics

# Product Information Dual Digital Current Regulator – CG208

Current Regulator ASIC for Automotive Transmission Control Units

#### **Customer benefits:**

- No end of assembly line adjustment necessary

- Easy application and straight adaptable to new solution

- Regulator with minimum of external components

- Hardware synergies by multi-channel application (synchronization)

- No need for µC real time computing power for current regulators

- Frequency controlled valves for best EMC performance

- High safety level due to sophisticated diagnosis features and µC autonomous fail safe action

- Power stage temperature under control

- High quality, high robustness design & package

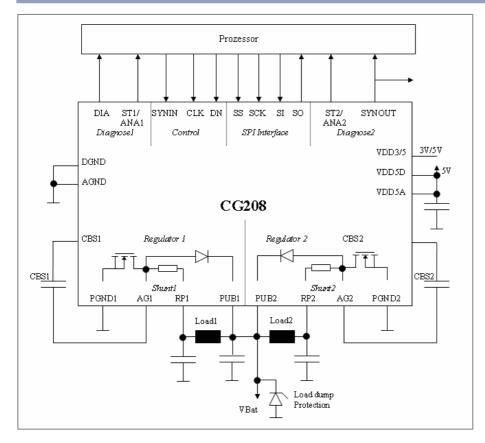

The CG208 is a fully integrated digital two-channel current regulator. Each channel comprises a digital regulator, low-side power switch, a freewheeling diode and a shunt resistor. A complete current regulator can be established with a minimum number of external components.

The load current is sensed by the internal shunt and the voltage drop is digitized by an integrated A / D converter.

The power stage is switched with constant frequency and variable duty cycle. The load current is sensed entirely in both switch phases.

A digital current regulation circuitry compares the actual shunt current with the target current value and controls the duty cycle of the low-side power switch with a programmable cycle frequency. Also the settling- and regulation time constants are set via a SPI interface. This allows the software to adopt the regulator characteristics to changing ambient conditions.

A diagnosis circuitry in each channel reports error conditions via SPI register. Additionally a digital error output as direct output pin reports the occurrence of an error. Alternatively each channel can operate as a processor controlled power switch bypassing the internal current regulator.

## Features

- High precision regulation ±1% at 1.2 A, 25°C

- High precision over of hole temperature range: TQFP\_epad:  $-40^{\circ}C \le T_{J} \le 150^{\circ}C$ Bare die:  $-40^{\circ}C \le T_{J} \le 175^{\circ}C$

- High current resolution (Δ = 0.6mA) over the current regulation range from 0.6mA to 1228mA

- Wide battery voltage range from 6.3 V to 43 V

- Daisy chain frequency synchronization

- Software adjustable a)power stage cycle frequency

b) integrator control time c) regulator step response and fast settling features

- Fully programmable sinusoidal dither function

- Current measurement can be accessed via SPI and via analog values

- Self protected power stage via over current limiter and additional over current/temperature shut down

- Extra PIN for report error status for interrupt action and various diagnostics via fast 4 MHz SPI

- 3 V / 5 V compatible digital I / O pins

- Optional use as processor controlled power switch

- Package: TQFP44\_epad & bare die

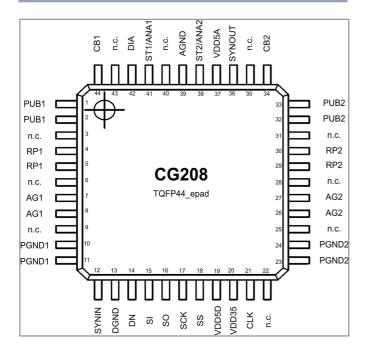

## **PIN configuration**

Picture: Pin Configuration package TQFP44\_epad V2.00

## Maximum ratings

| Parameter                      | Min  | Max | Unit |

|--------------------------------|------|-----|------|

| Supply voltage PUB1, PUB2      | -0.3 | 42  | V    |

| Supply voltage VDD5A, VDD5D    | -0.3 | 5.5 | V    |

| Supply voltage, VDD35          | -0.3 | 5.5 | V    |

| Supply current, VDD5A, VDD35   |      | 9.0 | mA   |

| Operating junction temperature |      |     |      |

| bare die                       | - 40 | 175 | °C   |

| TQFP                           | - 40 | 150 | °C   |

| ESD HBM 100pF / 1.5k           |      |     |      |

| power stage                    | - 4  | + 4 | kV   |

| all other pins                 | - 2  | + 2 | kV   |

## **Functional description**

| Pin                             | Name  | Function                                                      |  |  |

|---------------------------------|-------|---------------------------------------------------------------|--|--|

| Control / Power stage Channel 2 |       |                                                               |  |  |

| 1,2                             | PUB1  | Battery supply connector, cathode of the freewheel diode.     |  |  |

| 7,8                             | AG1   | Output low side power stage 1, negative CBS1-connection       |  |  |

| 4,5                             | RP1   | Load connector in Regulation Mode.                            |  |  |

| 44                              | CB1   | Positive connector for the bootstrap-<br>capacitor channel 1. |  |  |

| 10,11                           | PGND1 | Ground connector of power stage1.                             |  |  |

| Control / Power stage Channel 2 |       |                                                               |  |  |

| 32,33                           | PUB2  | Battery supply connector, cathode of the freewheel diode.     |  |  |

| 26,27                           | AG2   | Output low side power stage 1,<br>negative CBS2-connection    |  |  |

| 29,30                           | RP2   | Load connector in Regulation Mode.                            |  |  |

| 34                              | CBS2  | Positive connector for the bootstrap-<br>capacitor channel 2. |  |  |

| 23,24                           | PGN2  | Ground connector of power stage2.                             |  |  |

| Pin      | Name                            | Function                                                 |  |  |  |  |  |

|----------|---------------------------------|----------------------------------------------------------|--|--|--|--|--|

| Contro   | Control / Power stage Channel 2 |                                                          |  |  |  |  |  |

|          |                                 | Battery supply connector, cathode of                     |  |  |  |  |  |

| 1,2      | PUB1                            | the freewheel diode.                                     |  |  |  |  |  |

| 7.0 4.01 |                                 | Output low side power stage 1,                           |  |  |  |  |  |

| 7,8      | AG1                             | negative CBS1-connection                                 |  |  |  |  |  |

| 4,5      | RP1                             | Load connector in Regulation Mode.                       |  |  |  |  |  |

| 44       | CB1                             | Positive connector for the bootstrap-                    |  |  |  |  |  |

|          | CDI                             | capacitor channel 1.                                     |  |  |  |  |  |

| 10,11    | PGND1                           | Ground connector of power stage1.                        |  |  |  |  |  |

| Contro   | Control / Power stage Channel 2 |                                                          |  |  |  |  |  |

| 32,33    | PUB2                            | Battery supply connector, cathode of                     |  |  |  |  |  |

|          | 1 ODZ                           | the freewheel diode.                                     |  |  |  |  |  |

| 26,27    | AG2                             | Output low side power stage 1,                           |  |  |  |  |  |

|          | Auz                             | negative CBS2-connection                                 |  |  |  |  |  |

| 29,30    | RP2                             | Load connector in Regulation Mode.                       |  |  |  |  |  |

| 34       | CBS2                            | Positive connector for the bootstrap-                    |  |  |  |  |  |

|          |                                 | capacitor channel 2.                                     |  |  |  |  |  |

| 23,24    | PGN2                            | Ground connector of power stage2.                        |  |  |  |  |  |

| Voltage  | e supply                        |                                                          |  |  |  |  |  |

| 37       | VDD5A                           | Analog supply 5V, external connection                    |  |  |  |  |  |

|          | VDD3A                           | to VDD5D                                                 |  |  |  |  |  |

| 39       | AGND                            | Analog ground for analog supply                          |  |  |  |  |  |

|          | AGIND                           | (reference signal inputs)                                |  |  |  |  |  |

| 19       | VDD5D                           | Digital supply 5V, external connection                   |  |  |  |  |  |

|          |                                 | to VDD5A                                                 |  |  |  |  |  |

| 20       | VDD35                           | I/O Supply 5V or 3,3V                                    |  |  |  |  |  |

| 13       | DGND                            | Digital ground for the digital supply                    |  |  |  |  |  |

|          | 5 615                           | (reference SYNIN, SPI, DN)                               |  |  |  |  |  |

| 37       | VDD5A                           | Analog supply 5V, external connection                    |  |  |  |  |  |

|          |                                 | to VDD5D                                                 |  |  |  |  |  |

| Diagno   | sis / SPI Ir                    |                                                          |  |  |  |  |  |

|          | SYNIN                           | Synchronization input of oscillator,                     |  |  |  |  |  |

| 12       |                                 | positive edge-triggered, pullup current                  |  |  |  |  |  |

|          |                                 | source                                                   |  |  |  |  |  |

| 14       | DN                              | Reset input, active low, pulldown                        |  |  |  |  |  |

|          |                                 | current source<br>Slave-select-signal for SPI-interface, |  |  |  |  |  |

| 18       | SS                              | pullup current source                                    |  |  |  |  |  |

|          |                                 | Serial-clock-input (SPI-cycle input),                    |  |  |  |  |  |

| 17       | SCK                             | pullup current source                                    |  |  |  |  |  |

|          |                                 | Slave-in-signal (data input of SPI-                      |  |  |  |  |  |

| 15       | SI                              | interface), pullup current source                        |  |  |  |  |  |

|          |                                 | Slave-out-signal (data output of SPI-                    |  |  |  |  |  |

| 16       | SO                              | interface), tri-State                                    |  |  |  |  |  |

|          |                                 | External 2MHz clk-intake, pullup                         |  |  |  |  |  |

| 21       | CLK                             | current source                                           |  |  |  |  |  |

| 42       | DIA                             | Status of both channel                                   |  |  |  |  |  |

| 36       | SYNOUT                          | SYNOUT output                                            |  |  |  |  |  |

|          | ST1/                            | Status output 1/ Analog output of                        |  |  |  |  |  |

| 41       | ANA1                            | actual load current 1                                    |  |  |  |  |  |

| 00       | ST2/                            | Status output 2 / Analog output of                       |  |  |  |  |  |

| 38       | ANA2                            | actual load current 2                                    |  |  |  |  |  |

|          |                                 |                                                          |  |  |  |  |  |

The CG208 has self protecting functions for each channel. Detection of over temperature or over current condition shuts down the concerning low side switch.

Every single error occurrence of each channel will be filtered and registered and can be examined by SPI communication, such as:

- Over temperature

- Over current

- Short to ground

- Open load

- Clock error

If at least one error bit is set, the open drain error flag ST is driven low.

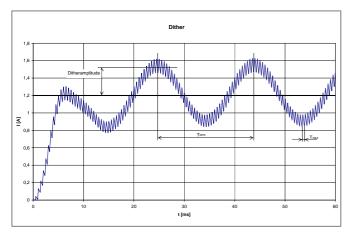

#### Dither

Each current regulator channel has its own dither generator. The generator can superimpose a sine wave on the target current. The dither frequency and amplitude can be programmed through the dither frequency register DFRx register and dither amplitude register DAMx separately for each channel. The regulator takes care that the actual dither amplitude is always smaller than the target current without effecting the Dither amplitude register.

Picture: Dither amplitude and frequency

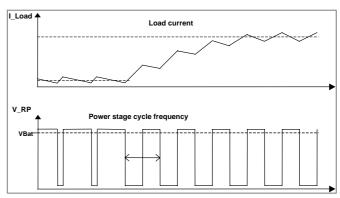

## **Typical startup**

Picture: Constant frequency and variable duty cycle

### **Power stage**

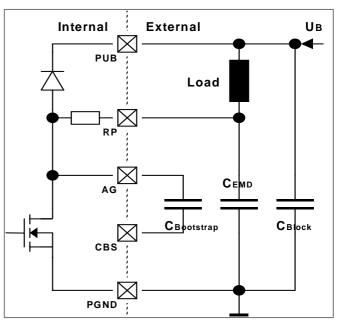

Picture: Power Stage V1.00

| Parameter                                    | Min | Max    | Unit |

|----------------------------------------------|-----|--------|------|

| Supply voltage, PUB1, PUB2                   | 6.3 | 43     | V    |

| High accuracy                                | 6.3 | 20     | V    |

| reduced accuracy                             | 20  | 30     | V    |

| ISO Pulse                                    | 30  | 43     | V    |

| Regulation target range                      | 0.6 | 1228   | mA   |

| Regulation target accuracy                   |     | 1.2    | mA   |

| Regulation current accuracy                  |     |        |      |

| 20°C 1.2 A                                   |     | ± 1    | %    |

| $-40^{\circ}C \leq T_{J} \leq +150^{\circ}C$ |     |        |      |

| Target regulation current                    |     | + 1.25 | %    |

| accuracy > 500 mA                            |     | ± 1.25 | /0   |

| Target regulation current                    |     | ± 8    | mΑ   |

| accuracy $\leq 500 \text{ mA}$               |     | ± 0    | IIIA |

| Internal shunt resistance                    |     | 0.5    | Ohm  |

| Internal FET resistance, Rdson               |     | 0.3    | Ohm  |

| Cycle frequency, CLK = 2 MHz                 | 30  | 3960   | Hz   |

| Dither frequency                             | 0   | 780    | Hz   |

| Dither amplitude                             | 0   | 290    | mA   |

| External CBS bootstrap                       | 100 | 4700   | nF   |

| capacitance                                  | 100 | 4700   | IIF  |

Picture: Application Diagram V2.00

## Contact

Robert Bosch GmbH Sales Semiconductors Postbox 13 42 72703 Reutlingen Germany Tel.: +49 7121 35-2179 Fax: +49 7121 35-2170 Robert Bosch Corporation Component Sales 38000 Hills Tech Drive Farmington Hills, MI 48331 USA Tel.: +1 248 876-7441 Fax: +1 248 848-2818 Robert Bosch K.K. Component Sales 9-1, Ushikubo 3-chome Tsuzuki-ku, Yokohama 224 Japan Tel.: +81 45 9 12-83 01 Fax: +81 45 9 12-95 73

#### E-Mail: bosch.semiconductors@de.bosch.com

Internet: www.bosch-semiconductors.com

© 07/2007 All rights reserved by Robert Bosch GmbH including the right to file industrial property rights Robert Bosch GmbH retains the sole powers of distribution, such as reproduction, copying and distribution. For any use of products outside the released application, specified environments or installation conditions no warranty shall apply and Bosch shall not be liable for such products or any damage caused by such products.