## **Automotive Electronics**

# **Product Information 4-Loop Firing IC – CG984**

#### **Customer benefits:**

- Excellent system know-how

- Smart concepts for system safety

- Secured supply

- Long- term availability of manufacturing processes and products

- QS9000 and ISO/TS16949 certified

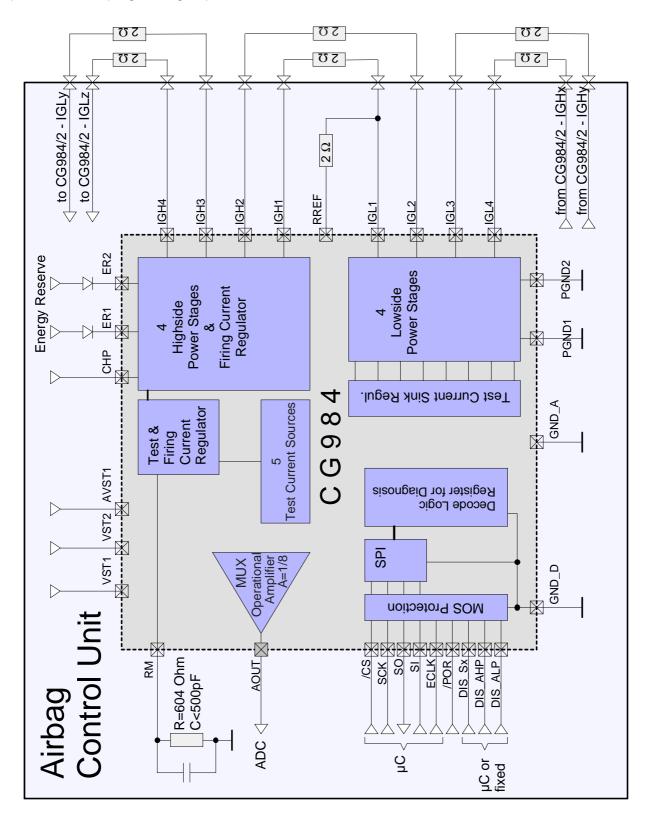

Following the successful implementation of the CG685/CG687 Quad- and Dual Firing Loop ICs, Bosch Automotive Electronics will move along with the introduction of a new generation of a Quad Firing IC for DC firing, CG984, fully compatible to the new 8 channel squib driver CG988. The CG984 is being designed by utilizing leading-edge automotive ASIC processes with 0.8µm feature size. The superior performance with respect to precision and reliability and the well-proven safety concept of its predecessors will be combined with a variety of new features as required by the quickly evolving next generations of electronic safety systems.

#### **Features**

- Optimized firing concept with 2 firing modes for efficient energy management

- Firing current >2A for 3ms, single pulse

- Energy reserve voltage up to 35V

- Full cross coupling capability (highside and lowside drivers placed on different ASICs)

- Firing current counter, 4 bit per firing loop

- High precision firing loop diagnostics (shorts, leakage, squib resistance)

- 15 channel analog multiplexer with tristate mode to monitor squib pins and supply voltages

- Sophisticated safety concept (power-on reset, disable pins for highside and for lowside stages, redundant firing path circuitry)

- 3 safety disable pins to lock 3 groups of up to 4firing-loops

- All functions controlled via 8MHz, 16 bit bidirectional SPI

- 5V/3.3V systems compatibility

- QFP44 package

(Example for cross coupling of firing loops 3-4 shown)

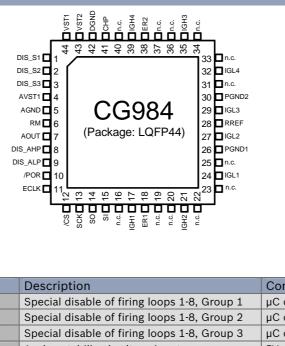

### Pin description

| No | Name          | Class. | Description                                  | Comments / Recommended Circuit        |

|----|---------------|--------|----------------------------------------------|---------------------------------------|

| 1  | DIS_S1        | In     | Special disable of firing loops 1-8, Group 1 | μC or fixed                           |

| 2  | DIS_S2        | In     | Special disable of firing loops 1-8, Group 2 | μC or fixed                           |

| 3  | DIS_S3        | In     | Special disable of firing loops 1-8, Group 3 | μC or fixed                           |

| 4  | AVST1         | Supply | Analog stabilised voltage input              | 5V                                    |

| 5  | AGND          | Supply | Analog ground                                | GND                                   |

| 6  | RM            | In     | Test current adjust                          | 604Ω ± 1%, C<500pF                    |

| 7  | AOUT          | Out    | Analog multiplexer output                    | μC, A/D                               |

| 8  | DIS_AHP       | In     | Disable all highside power stages            | μC                                    |

| 9  | DIS_ALP       | In     | Disable all lowside power stages             | μC                                    |

| 10 | /POR          | In     | Power on reset, active low                   | RESET circuit                         |

| 11 | ECLK          | In     | External clock, 2 MHz                        | μC, Clock 2MHz                        |

| 12 | /CS           | In     | Chip select                                  | μC, SPI                               |

| 13 | SCK           | In     | Serial clock, 8MHz                           | μC, SPI, Clock 8MHz max.              |

| 14 | SO            | Out    | Slave out                                    | μC, SPI                               |

| 15 | SI            | In     | Slave in                                     | μC, SPI                               |

| 16 | Not connected |        |                                              |                                       |

| 17 | IGH1          | Out    | Igniter loop high, channel 1                 | Squib loop 1, highside                |

| 18 | ER1           | Supply | Energy reserve voltage firing loop 1,2       | 33V±2V, energy reserve                |

| 19 | Not connected |        |                                              |                                       |

| 20 | Not connected |        |                                              |                                       |

| 21 | IGH2          | Out    | Igniter loop high, channel 2                 | Squib loop 2, highside                |

| 22 | Not connected |        |                                              |                                       |

| 23 | Not connected |        |                                              |                                       |

| 24 | IGL1          | In     | Igniter loop low, channel 1                  | Squib loop 1, lowside                 |

| 25 | Not connected |        |                                              |                                       |

| 26 | PGND1         | Supply | Power ground firing loop 1,2                 | GND                                   |

| 27 | IGL2          | In     | Igniter loop low, channel 2                  | Squib loop 2, lowside                 |

| 28 | RREF          | Out    | Reference resistor                           | Expected total firing loop resistance |

| 29 | IGL3          | In     | Igniter loop low, channel 3                  | Squib loop 3, lowside                 |

| 30 | PGND2         | Supply | Power ground firing loop 3,4                 | GND                                   |

| 31 | Not connected |        |                                              |                                       |

| 32 | IGL4          | In     | Igniter loop low, channel 4                  | Squib loop 4, lowside                 |

| 33 | Not connected |        |                                              |                                       |

| 34 | Not connected |        |                                              |                                       |

| 35 | IGH3          | Out    | Igniter loop high, channel 3                 | Squib loop 3, highside                |

| 36 | Not connected |        |                                              |                                       |

| 37 | Not connected |        |                                              |                                       |

| 38 | ER2           | Supply | Energy reserve voltage firing loop 3,4       | 33V±2V, energy reserve                |

| 39 | IGH4          | Out    | Igniter loop high, channel 4                 | Squib loop 4, highside                |

| 40 | Not connected |        |                                              |                                       |

| 41 | CHP           | Supply | Charge pump voltage                          | VERx+7V                               |

| 42 | DGND          | Supply | Digital ground                               | GND                                   |

| 43 | VST2          | Supply | Digital 3.3V/5V stabilized voltage input     | 3.3V/5V (according to mC)             |

| 44 | VST1          | Supply | Digital 5V stabilized voltage input          | 5V                                    |

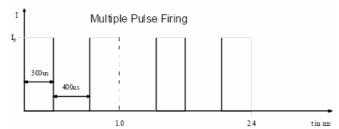

#### **Dual Firing Mode Concept**

The CG984 operates in two different firing modes depending on the energy reserve voltage at pins ER1-ER2 (the proper firing mode is set by the CG984 and is not accessible by SPI command). Starting the firing sequence with an energy reserve voltage of 35V, CG984 fires with multiple pulses at high current level for an efficient energy management. The nominal firing current is 3A. As the energy reserve voltage falls beyond VER(nom)=23.5V the second mode (single pulse firing mode) is enabled with a minimal firing current of 2A. The reduced firing current for single pulse ensures full energy for the squib down to low energy reserve voltages. The pulse mode of the selected loop is determined by the ASIC and remains unchanged during the complete firing sequence. The gain in efficiency in comparison to conventional DC firing concepts is in the range of 20 to 25 percent. The dual firing mode concept operates without any additional effort by  $\mu$ C.

To ensure an optimized firing of both high energy and low energy squibs two different time frames are defined: 1ms for low energy squibs and 2.5ms for their high energy counterparts. The firing sequence can be extended up to 3ms with full short circuit protection.

#### Multiple pulse firing

VER(nom) • 23.5 V

IP: 2.55A ... 3.45A, nominal 3.0A Firing time adjustable by software.

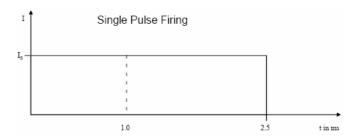

#### Single pulse firing

VER(nom) < 23.5 V

Is: 2.0A ... 2.8A, nominal 2.4A

Firing time adjustable by software.

#### **Maximum ratings**

| Parameter                      | Symbol             | Min.  | Тур. | Max. | Unit |

|--------------------------------|--------------------|-------|------|------|------|

|                                | VER1-2             | -0.3  |      | 36   | V    |

|                                | Vснр               | -0.3  |      | 36   | V    |

| Supply voltages                | VvsT1              | -0.3  |      | 7    | V    |

|                                | V <sub>AVST1</sub> | -0.3  |      | 7    | V    |

|                                | Vvst2              | -0.3  |      | 7    | V    |

| Power ground                   | VpgND12            | -0.3  |      | 0.3  | V    |

| Digital ground                 | VDGND              | -0.3  |      | 0.3  | V    |

|                                | Vigh14             | -0.3  |      | 36   | V    |

| Firing loops, static           | Vigl14             | -0.3  |      | 36   | V    |

|                                | VRREF              | -0.3  |      | 36   | V    |

| Junction temperature           | Tj                 | -40   |      | 150  | °C   |

| Operating temperature          | T <sub>amb</sub>   | -40   |      | 105  | °C   |

| ESD classification             |                    |       |      |      |      |

| - Human body, C=100pF, R=1.5kΩ | Vнвм               | -2000 |      | 2000 | V    |

#### **Electrical characteristics**

| Parameter       | Symbol             | Min.                  | Тур.     | Max.     | Unit |

|-----------------|--------------------|-----------------------|----------|----------|------|

|                 | V <sub>ER1</sub>   | 10                    |          | 35       | V    |

|                 | VER2-4             | 5.2                   |          | 35       | V    |

| Supply voltages | V <sub>CHP</sub>   | V <sub>ERmin</sub> +7 |          | 35       | V    |

| Supply voltages | VvsT1              | 4.7                   | 4.9      | 5.1      | V    |

|                 | V <sub>AVST1</sub> | 4.7                   | 4.9      | 5.1      | V    |

|                 | Vvst2              | 3.1/4.7*              | 3.3/4.9* | 3.5/5.1* | V    |

$Rsquib=2\Omega$

| Parameter                                                                                               | Symbol               | Min. | Тур.    | Max.     | Unit |  |

|---------------------------------------------------------------------------------------------------------|----------------------|------|---------|----------|------|--|

| Current reference                                                                                       | R <sub>RM</sub>      |      | 604     |          | Ω    |  |

| (AVST1=4.9V)                                                                                            | Irm                  | -4%  | 2       | 4%       | mA   |  |

| Test current source                                                                                     |                      |      |         |          |      |  |

| Ratio test/ reference current, IRM=2mA                                                                  | Irref/Irm            | 18.5 | 19.75   | 21       |      |  |

| Tracking of test current source, 0≤V <sub>IGH</sub> ≤0.5V                                               | lіgнx/lіgну          | 0.99 | 1.00    | 1.1      |      |  |

| Test current sink                                                                                       |                      |      |         |          |      |  |

| Saturation voltage, IIGL=40mA                                                                           | VigL                 | 10   | 20      | 40       | mV   |  |

| Tracking of saturation voltage, lowside                                                                 | Viglx/Vigly          | -20% | 1       | 20%      |      |  |

| Current limitation,<br>VIGL<18V, t<3ms                                                                  | ligL                 | 60   | 120     | 180      | mA   |  |

| Voltage divider at IGLx, IGHx                                                                           |                      |      |         |          |      |  |

| Pull up resistor for leakage tests                                                                      | Righx,Riglx          | 6    | 12      | 20       | kΩ   |  |

| Pull down resistor for leakage tests                                                                    | Righx,Riglx          | 3    | 6       | 10       | kΩ   |  |

| Quiescent potential                                                                                     | Vighx,Viglx          | -5%  | AVST1/3 | 5%       | V    |  |

| Highside power stage                                                                                    |                      |      |         |          |      |  |

| Firing current (ton ≤ 3ms, Ver ≤ 35                                                                     | iV)                  |      |         |          |      |  |

| Switching voltage between firing modes                                                                  | Vsw                  | 22   | 23.5    | 25       | V    |  |

| Pulse mode, VER>VSW                                                                                     | -lighx               | 2.55 | 3.0     | 3.45     | A    |  |

| Single pulse mode, VER <vsw< td=""><td>-lighx</td><td>2.0</td><td>2.4</td><td>2.8</td><td>A</td></vsw<> | -lighx               | 2.0  | 2.4     | 2.8      | A    |  |

| Duty cycle, pulse mode, error<1%                                                                        |                      | 41.5 | 43      | 50       | %    |  |

| Drain-source on-state resistance (TJ≤105°C, IDS=0.5A)                                                   | RDS(on)              |      | 0.8     | 1.2      | Ω    |  |

| Drain-source voltage (TJ≤105°C, IDS=2A)                                                                 | V <sub>DS(min)</sub> |      |         | 3        | V    |  |

| Lowside power stage                                                                                     |                      |      |         |          |      |  |

| Firing current (ton $\leq 2.5$ ms, Ver $\leq 35$ V)                                                     |                      |      |         |          |      |  |

| Current load capacity (TJ≤105°C)                                                                        | liglx                | 3.5  |         |          | A    |  |

| Drain-source on-state resistance                                                                        | RDS(on)              |      | 0.6     | 1.0      | Ω    |  |

| (TJ≤105°C, IDS=0.5A)                                                                                    |                      |      |         |          |      |  |

| Drain-source voltage (TJ≤105°C, IDS=2A)                                                                 | V <sub>DS(min)</sub> |      |         | 3        | V    |  |

| Firing current detection level                                                                          |                      |      |         |          |      |  |

| Ver-Vigh>5V                                                                                             |                      |      |         |          |      |  |

| Multiple pulse mode                                                                                     | IFDET(MP)            | 1.5  |         | IREG(MP) | A    |  |

| Single pulse mode                                                                                       | IFDET(SP)            | 1.2  |         | IREG(SP) | A    |  |

<sup>\*</sup> VvsT2 in 5V System environment

E-Mail: <u>bosch.semiconductors@de.bosch.com</u>

#### Contact

Robert Bosch GmbH Sales Semiconductors Postbox 13 42 72703 Reutlingen Germany

Tel.: +49 7121 35-2979 Fax: +49 7121 35-2170 Robert Bosch Corporation Component Sales 38000 Hills Tech Drive Farmington Hills, MI 48331 USA

Tel.: +1 248 876-7441 Fax: +1 248 848-2818 Robert Bosch K.K. Component Sales 9-1, Ushikubo 3-chome Tsuzuki-ku, Yokohama 224 Japan

Tel.: +81 45 9 12-83 01 Fax: +81 45 9 12-95 73

Internet: www.bosch-semiconductors.de

© **03/2006** All rights reserved by Robert Bosch GmbH including the right to file industrial property rights Robert Bosch GmbH retains the sole powers of distribution, such as reproduction, copying and distribution.

For any use of products outside the released application, specified environments or installation conditions no warranty shall apply and Bosch shall not be liable for such products or any damage caused by such products.

<sup>\*\*</sup> measured with reduced accuracy; guarantied by design